Hvordan lage en enkel seriell UART-sender i verilog HDL

De fleste Universal Asynchronous Receiver Transmitter (UART) som jeg fant på nettet, er for kompliserte og vanskelige å forstå, her vil jeg forklare noen enkle teorier og også kode om hvordan man bygger en.

La oss først snakke om hvordan sendere fungerer. Det grunnleggende prinsippet er å sende flere databiter over en enkelt linje. I senderen vår er disse dataene parallelle, men for å redusere antall kabler som kreves, bruker vi seriell kommunikasjon som blir konvertert til parallell i mottakersiden.

De grunnleggende tingene vi trenger er følgende:

- En klokkedeler (vår teller)

Dette gjør at vi kan sende data med en viss hastighet (baudrate). Mottakeren vil prøve og ta dataene bit for bit.

- Et skiftregister

Vi trenger å vite hvor mange biter om gangen vi sender, vårt skiftregister vil ha en startbit, databiter, paritetsbit (valgfri), sluttbit.

- Et tilstandsdiagram

Før vi skriver noen kode, må vi tenke på hva vi trenger å lage, og den beste måten er å lage et tilstandsdiagram over designet vårt. Vi vet at for en sender trenger vi to tilstander, tomgang og overføring.

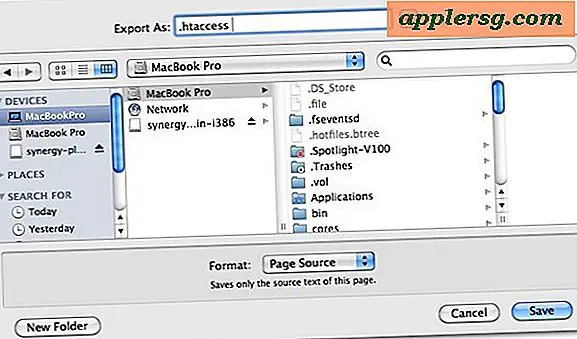

Etter å ha hatt et tilstandsdiagram, kan vi nå beregne hva telleren vår vil være. Dette gjøres ved å bruke:

teller = FPGA klokkehastighet / baudrate

I dette eksemplet bruker jeg en baudrate på 9600, noe som gjør telleren min = 5208.

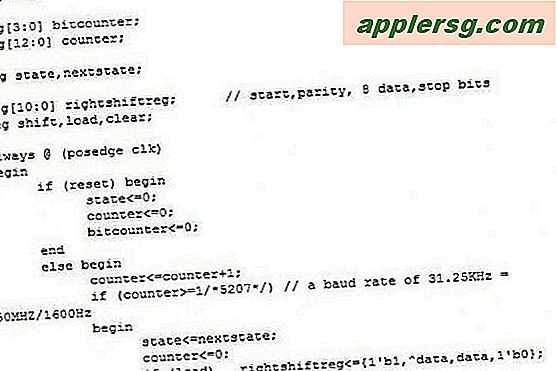

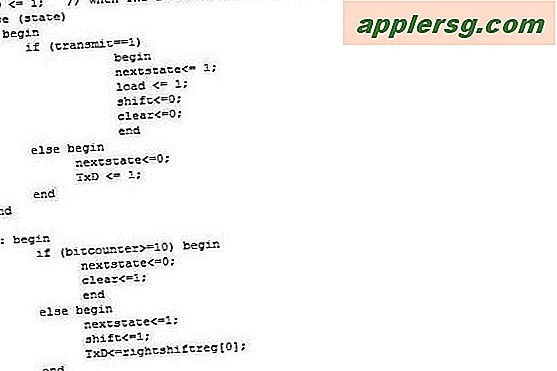

Til slutt beregner vi skiftregisteret vårt og fullfører skrivingen av statsmaskinen vår. I eksempelkoden min bruker jeg startbit, paritetsbit, 8 bits data og sluttbit. Dette er totalt 11 biter.

Begge bildene i trinn 2 og 3 sammen i samme modul fullfører senderkoden som kreves for å programmere til FPGA. Denne koden vil fungere med en annen FPGA koblet serielt eller med windows hyperterminal blant annet maskinvare. Kan lett modifiseres for å jobbe med mye mer.

Til slutt oppretter vi en testarmatur for å fikse eventuelle feil og simulere programmet vårt før vi programmerer FPGA.

Dette avslutter senderen. Legg igjen kommentarer hvis du har spørsmål eller føler at det mangler noe her.

Tips

Både sender og mottaker må vite baudhastigheten som data sendes til.